博文

JLPEA 交错多线程RISC-V核心中动态三模冗余的评估  精选

精选

||

在当今高度依赖电子设备的社会中,确保计算系统的可靠性和容错能力至关重要。特别是在航空航天、医疗设备和汽车电子等关键领域,系统需要在面对各种故障时仍能保持正常运行。为此,研究人员不断探索新的方法来增强处理器的容错能力。来自意大利罗马大学信息工程、电子和电信系的Mauro Olivieri教授团队,在 Journal of Low Power Electronics and Applications (JLPEA) 上发表了研究论文,提出了一种在交错多线程RISC-V核心中实现动态三模冗余 (DTMR) 的方法,为提高处理器的可靠性提供了新的思路。

研究过程与结果

随着半导体技术的进步,电子设备的集成度和复杂性不断提高,但这也使得系统更容易受到软错误的影响。软错误是指由于高能粒子撞击或其他环境因素导致的瞬态故障,虽然不会对硬件造成永久性损害,但可能会引起数据错误或系统崩溃。为应对这一挑战,三模冗余 (TMR) 技术被广泛应用。TMR通过将关键组件三重化,并对其输出进行投票,以检测和纠正错误,从而提高系统的容错能力。然而,传统的TMR实现需要三倍的硬件资源,成本高昂且功耗增加。因此,如何在有限的资源下实现高效的容错机制成为研究的热点。

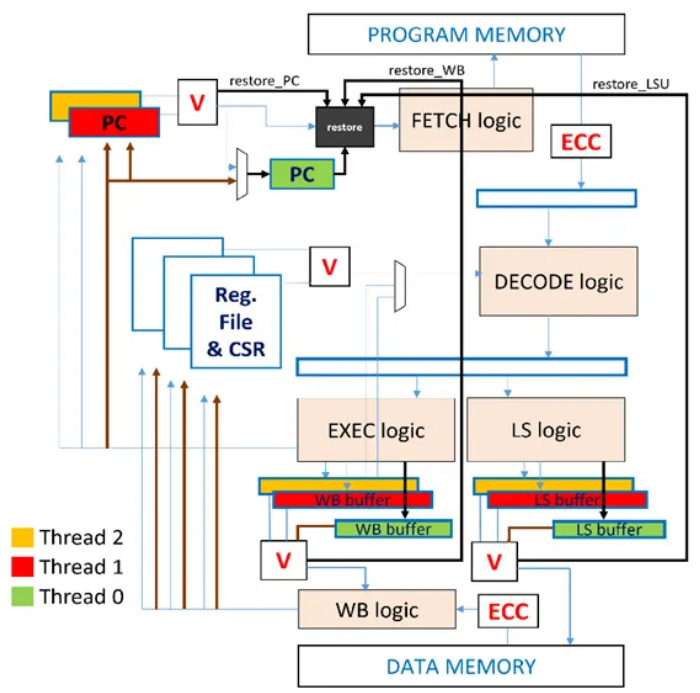

本文提出了一种动态三模冗余 (DTMR) 方法,在作者命名为Klessydra-dfT03的新核心中实现,该方法可有效地将TMR与交错多线程 (IMT) 技术相结合,以降低资源开销。具体而言,作者在RISC-V处理器核心中引入了三条独立的线程,这些线程以交错的方式执行相同的指令流。通过在每个时钟周期执行不同线程的指令,实现了指令级的冗余。当三个线程的输出不一致时,系统可以通过投票机制检测并纠正错误。这种方法利用了多线程的并行性,在提高容错能力的同时,避免了传统TMR对硬件资源的三倍需求。

为了验证所提出方法的有效性,作者在开源RISC-V处理器上实现了DTMR,并进行了广泛的实验测试。结果表明,在不显著增加硬件资源和功耗的情况下,DTMR能够有效检测和纠正软错误。与传统TMR相比,DTMR在资源利用率和能效方面具有明显优势。此外,实验还显示,DTMR对系统性能的影响较小,能够满足实时应用的需求。

Klessydra-dfT03微体系结构 (蓝色箭头:正常模式;黑色箭头:恢复模式;棕色箭头:结束恢复阶段)

研究总结

该研究展示了一种创新的容错方法,将动态三模冗余与交错多线程技术相结合,在提高系统可靠性的同时,降低了资源开销。这一方法为在资源受限的环境中实现高效的容错机制提供了新的可能性,对关键任务系统的设计具有重要的参考价值。DTMR方法特别适用于对可靠性要求高且资源有限的应用场景,如航空航天、医疗设备和汽车电子等。通过结合多线程技术和动态冗余,系统可以在不显著增加成本和功耗的情况下,提高对软错误的抵抗能力。未来,随着对高可靠性系统需求的增加,DTMR有望在更多领域得到应用和推广。

原文出自 JLPEA 期刊:https://www.mdpi.com/2079-9268/13/1/2

期刊主页:https://www.mdpi.com/journal/jlpea

JLPEA 期刊介绍

主编:Davide Bertozzi, University of Manchester, UK

期刊旨在发表低功耗电子方向的创新研究和重要成果。期刊范围涵盖的主题包括但不限于新兴电子器件和工艺技术、模拟、数字和混合信号VLSI电路、架构和系统设计、SoC和嵌入式系统、能量采集和无电池系统、综合和优化工具,以及用于低功耗设计的CAD工具和方法。目前被Scopus、ESCI (Web of Science) 等数据库收录。

2023 Impact Factor:1.6

2023 CiteScore:3.6

Time to First Decision:20 Days

Acceptance to Publication:2.7 Days

https://wap.sciencenet.cn/blog-3516770-1473714.html

上一篇:Surfaces 期刊首届青年编委招募——邀您共同促进学术期刊发展

下一篇:Applied Sciences 论文选题灵感:智能化与自动化技术及其应用