博文

处理器指令系统漫谈(8):频率

|||

DLX指令只出现在CAQA第一版和第二版用作教学之用,其指令助记符基本和MIPS相近,可以理解成MIPS的教学版。从CAQA第三版开始到第五版,DLX消失了,MIPS成为该教材的基础指令系统。

2003年的CAQA第三版终于在10年之后将Alpha指令系统写入了其RISC综述中,毕竟Alpha在业界有很大的影响,一直忽略总不好。如下图所示。

这个表在CAQA的第3-5版中一直没有发生过变化,其实这个表就是RISC的最主要的5个面向台式计算机和服务器计算机的主流RISC指令系统了。按时间顺序先来聊聊Alpha指令系统。

第一版Alpha AXP手册发表于1992年,Alpha是64位指令系统。1993年2月ACM旗舰杂志ACM通讯Communication of the ACM用了整整一期介绍alpha指令系统和相关的软硬件成果,气势宏大。这些文章在1992年已经在DEC刊物Digital Technical Journal的第4期发表过。【1】【2】

首先来看看Alpha指令系统设计的目标,DEC公司毕竟设计了VAX指令系统和PDP-11小型机,所以第4条无可厚非,在alpha指令系统中保留了VAX的浮点格式和一些指令,还要二进制兼容VAX和MIPS指令系统(DEC 用MIPS指令系统设计了个人工作站DECstation),所以动态二进制翻译机制被引入指令系统设计。兼容VAX的操作系统,所以有了PALCode指令。有点复杂了,历史包袱太沉重了。从这里也可以看出Alpha和MIPS的渊源颇深。

关于对高性能的分析,随后文章认为之前15-25年计算机的性能增长了1000倍,那么有理由认为今后20年计算机性能的增长仍然是1000倍。Alpha就是按照这个预想设计的。Alpha预计性能增长中10倍来源于频率、10倍来源于微体系结构(多发射等)、10倍来源于多处理机并行。后两个预测很值得期待和努力,但DEC关于频率的重视有待商榷。Alpha处理器在1990年代就能设计出GHz的处理器了。但到10年后的2003年,频率的增长停止了,Denard等比缩放定律逐渐失效了。到了现在25年后了,最高频率也就4GHz上下。

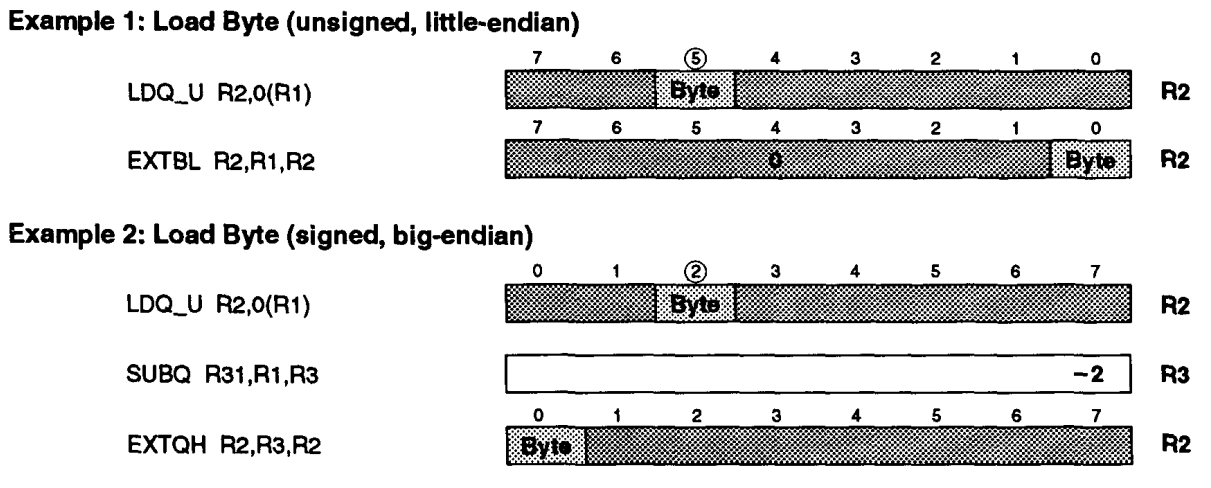

但是Alpha却为了高频率付出了巨大的指令系统面的努力。其中有一点为了减少Load的访问cache的延时,去掉了自动对齐的功能,如果你访问了非字对齐的字节或者半字,你需要两条指令,一条load接着一条移位指令,如果需要符号扩展,需要三条。

Alpha的寻址模式也只有一种,减少访存指令地址计算的延时,下图是CAQA中的RISC寻址模式比较。

Alpha指令系统体系结构不支持精确例外(Trap)。

所有这一切都是为了更高频率,为了更宽的发射宽度。也更严重的违背了组成无关、微结构无关、timing无关指令系统设计原则(IBM)。

将一些常见指令和寻址模式拆成更小的指令,用指令序列实现,增加了指令间的强相关,必须要采用更大的动态指令窗口来支持,利用率往往不高。后来Alpha为了提高整体性能追求多线程技术(提高计算资源利用率),最后21564进一步计划支持同时多线程(SMT),而多线程技术又对Cache和主存系统产生更高的要求,然后1990年代末的“存储墙”问题,然后是2000年代中期的“功耗墙”问题。一个又一个不断地打击着那些“极简”的RISC指令系统。

在这个时期,Intel凭借其强大的半导体工艺优势,也染上了频率综合征,Pentium4的流水线竟然20多级,L1 Cache竟然只有4KB。Intel后来和HP联合继续开发EPIC【3】,期望用编译技术来代替超标了的动态指令调度进一步提高频率,强推x86不兼容的Itanium技术,投了上千亿美金,后来就没有后来了,这样的编译太难做了。

2003年AMD推出兼容32位x86的AMD64(x86-64)的Opteron处理器之后,所有曾经的经典RISC处理器都不行了,最后只有IBM的Power v3.0(PowerPC+POWER)指令还有些市场(现在估计也不行了,开放了OpenPower)。Sparc归了Oracle封闭了,DEC被康柏收购后又被HP收购,而最终都被Intel吸收了。

1990年代中期到2000年代中期的“高频率就是高性能”现在看来更多是Intel出于商业竞争的考虑了,笔者不相信Intel不懂高性能不等于高频率这个事实。但用户不懂啊,你看intel的处理器性能就是比AMD的好,频率就是高,所以高频率等于高性能很合理啊。

在CAQA的书中,CPU性能公式一直贯穿前后。性能=1/执行时间=频率 x IPC(每周期完成执行指令数)/ 动态指令总数量。只追求频率而忽视IPC(多发射乱序执行的效率)和动态指令数(代码密度),是要付出历史代价的。

而Intel追求频率,x86是CISC代码密度低,Intel处理器微码最多3读操作数密度也不差,超标量技术其实大家都差不了太多,关键是自己有一堆集成电路芯片加工工厂,工艺技术至少领先1-2代,各种技术可以做纵向整合。所以Intel追求频率当时还是有点硬道理的,但也差点闪了腰,好在及时调整重归x86-64,大谈“高频率不等于高性能”,从此一统江湖。

来看看2001年的综述文章【4】中性能比较图,每MHz的Spec得分Alpha最低,一旦频率进步遇到瓶颈,就全凉了。而增加频率还有另一个缺点就是功耗,power=1/2aCV2f,有文章说电压和频率是相辅相成的,所以功耗的增加大概和频率成3次方的关系,盲目追求频率,功耗增加很大。而影响功耗的封装技术可是几十年变化很小,散热技术也是到这几年才敢大规模用上水冷。

在这方面RISC-V也是比较简单的指令系统,要引以为戒啊,找准定位,不要盲目自大妄想通吃啊。好在RISC-V支持一大堆的扩展指令,可以开发数据并行,而单指令功能比Alpha还是强一些,和MIPS接近。

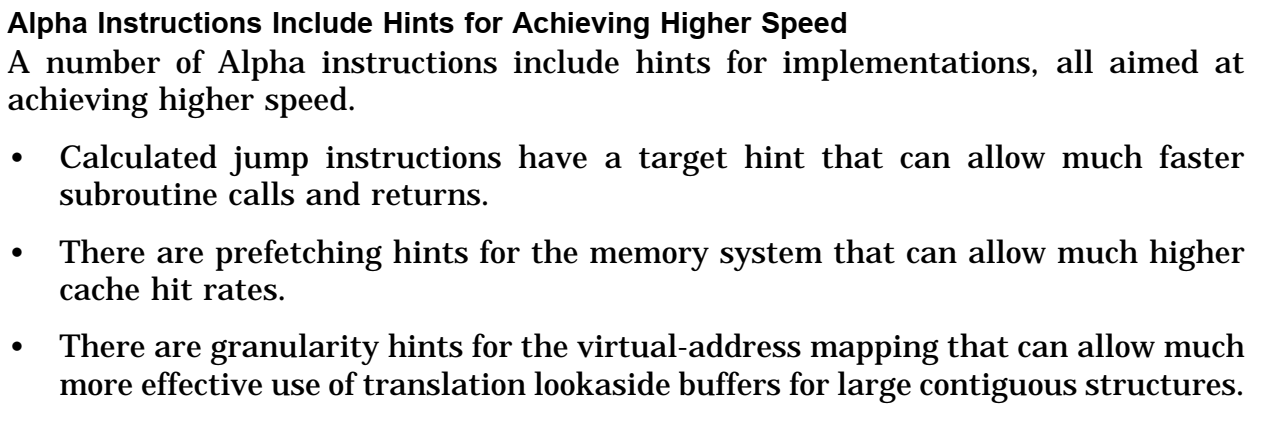

另外,在Alpha的手册里面有这样一段

与PA-RISC一样,Alpha指令系统也充分认识到了编译-微体系结构协作的重要性,在分支指令、Cache预取和TLB方面设计了丰富的hint机制。这个hint机制我们在设计新时代指令系统时应该重点关注。

【1】Richard, L. S. 1993. "Alpha AXP architecture." Communications of the ACM 36(2): 33-44.

【2】McLellan, E. 1993. "The Alpha AXP architecture and 21064 processor." Micro, IEEE 13(3): 36-47.

【3】Michael S. Schlansker and B. Ramakrishna Rau. 2000. “EPIC: Explicitly Parallel Instruction Computing”. Computer, IEEE 33(2): 37-45.

【4】Ronen, R., et al. and John P. Shen. 2001. "Coming challenges in microarchitecture and architecture." Proceedings of the IEEE 89(3): 325-340.

https://wap.sciencenet.cn/blog-102148-1195459.html

上一篇:处理器指令系统漫谈(7):大厂

下一篇:处理器指令系统漫谈(9):老大